Midterm 19/4/2016

#### **Question 1 (15)**

1- Describe PMOS, NMOS Explain how they work? I am not looking for ON/OFF answers. A discussion of the Vgs.Id curve and region of operation should ensue. (5points)

```

If Vds = 0,

Accumulation Vgs << Vt

Depletion

Vgs ~ Vt

Vgs > Vt

Inversion

If Vds >0,

Unsaturated Vgs - Vt > Vds

Saturation Vgs - Vt < Vds

Cutt-off Current flow is

Current flow is essentially zero.

```

- 2- How do you evaluate performance of a digital circuit, please name at least three? (3 points)

- a. Area/Cost

- b. Reliability

- Scalability

- d. Speed (delay, operating frequency)

- e. Power dissipation

- f. Energy to perform a function

- 2. Yield & Defects: What is the yield and how do we calculated? (2 points)

$$Y = \frac{\text{No. of good chips per wafer}}{\text{Total number of chips per wafer}} \times 100\%$$

- 3. What are the three types of power? (5 points)

- p(t) = v(t)i(t) = Vsupplyi(t)

- Peak power:

- Ppeak = Vsupplyipeak

- Average power:

$$P_{ave} = \frac{1}{T} \int_{t}^{t+T} p(t)dt = \frac{V_{supply}}{T} \int_{t}^{t+T} i_{supply}(t)dt$$

Midterm 19/4/2016

# Question 2 (25)

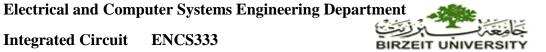

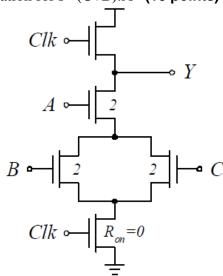

1. What type of logic function does these circuit do? (12 points)

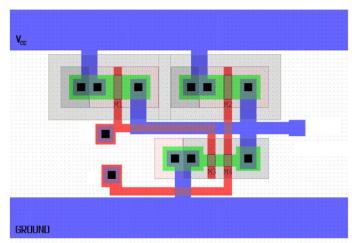

- 2. Given the truth table below, (8 points)

- 1- Draw the CMOS circuit in transistor level

- 2- Draw the layout stick diagram

| A | В | Out |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

3- Given a complex gate as shown below, what the function of the circuit? (5 points)

F=((A+B).C)

Midterm 19/4/2016

## Question 4 (25)

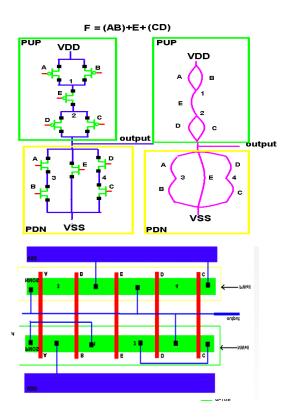

1. Draw the CMOS transistor level for this complex Gate and draw the stick diagram for it F=E+(AB)+CD(15 points)

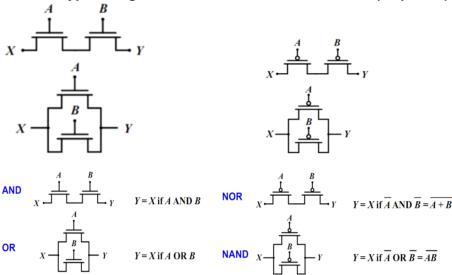

2. Consider the following figure below, what type of logic gate is this? Do you think the designer balance the rise and fall time? (10 points)

NAND2. The pull-up network has two PMOSFETs in parallel and the pulldown network has two NMOSFETs in series. Interestingly, we can see that the designer didn't balance tphl and tplh.

Midterm 19/4/2016

## Question 4 (25)

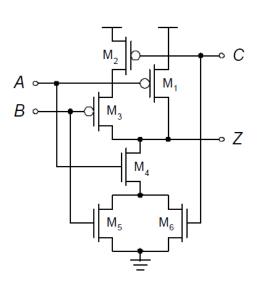

Draw static and dynamic implementation for F=(C+B).A (10 points)

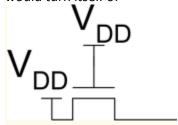

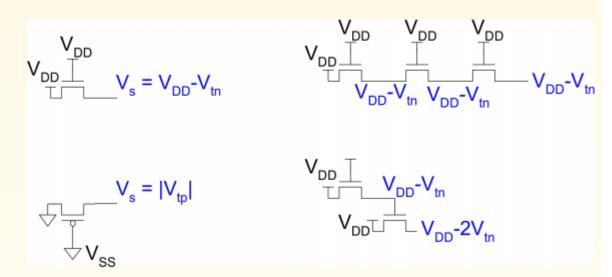

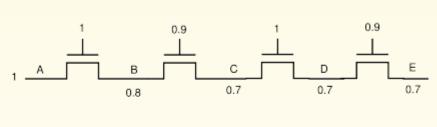

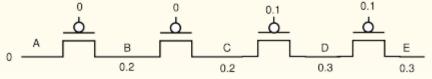

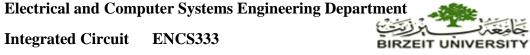

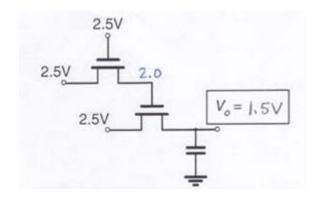

- 4- What is the output voltage of each of these devices: (15 points)

- If Vgd < Vt , channel pinches off near drain when Vds > Vdsat = Vgs Vt

$$I_{ds} = \left\{ \begin{array}{cccc} 0 & V_{gs} & < & V_t & \text{Cutoff} \\ \beta \left(V_{gs} - V_t - V_{ds}/2\right) V_{ds} & V_{ds} & < & V_{dsat} & \text{Linear} \\ \frac{\beta}{2} (V_{gs} - V_t)^2 & V_{ds} & > & V_{dsat} & \text{Saturation} \end{array} \right.$$

Example, pass transistor passing VDD Vg = VDD If Vs > VDD - Vt, Vgs < Vt Hence, transistor would turn itself of

ENCS333

**Integrated Circuit**

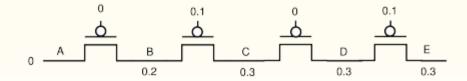

What would be the voltages on the different nodes?

Assume: initial voltage of 0.5V on all the internal nodes

$$V_{dd}=1.0V$$

,  $V_{t_n}=0.2V$  and  $|V_{t_p}|=0.2V$

Midterm

ENCS333

Midterm 19/4/2016

## Question 4 (10)

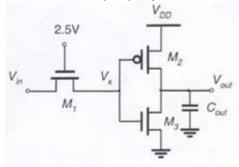

Consider a three trainsitor circuit as shown in figure below. Vdd=2.5V and input signal switch between 0 and Vdd with sharp rise and fall times. All transistor are minimum length 1=0.25UM, trainsestor width W2=2um, W1=1um. Note: ignore body effect. Find M3 transistor width such that the switching point of the inverter (Vm) is placed in the middle of Vx signal swing (10 points)

nent BIRZEIT UNIVERSITY

**Integrated Circuit** ENCS333

Vin = 2.5V

VX= VXH-VXL = 1.05V

At Vout=Vm, VDS=-1.45V for PMOS M2 and

VDS=1.05V for NMOS M3, which means both M2

and M3 are velocity Saturated (VDSATP=-1, VDSATN=0.6).

We know for the inverter IM2= IM3, so we can solve for the width of M3 using the velocity Saturated current equations.

\[

\begin{align\*}

\text{IDS3} & \text{Wn kn' VBSATN}(Vm-Vtn-\frac{VBSATN}{2}) \\

\text{IDSATP} & \text{WDSATP}((VDD-Vm)+Vtp+\frac{VBSATP}{2}) = 1

\end{align\*}

\]

\[

\text{WP} & \text{kn' VDSATP}((VDD-Vm)-Vtp-\frac{VBSATP}{2}) = 1.46; \text{Wn} = \frac{W2}{1.46} \simeq 1.37 \text{µm}

\]